## ECE680: Physical VLSI Design

#### Chapter III

CMOS Device, Inverter,

Combinational circuit Logic and Layout

Part 3 Combinational Logic Gates (textbook chapter 6)

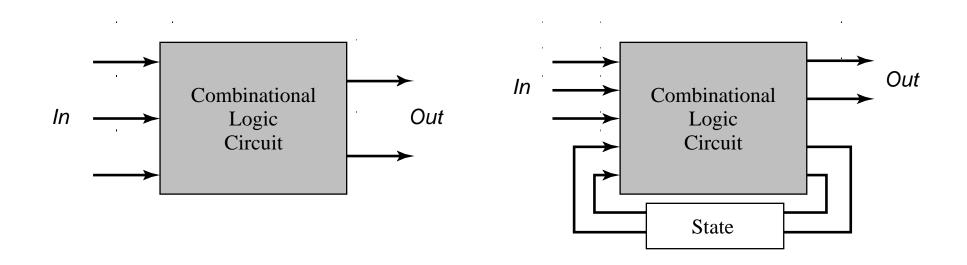

#### Combinational vs. Sequential Logic

Combinational

Sequential

Output = f(In)

Output = f(In, Previous In)

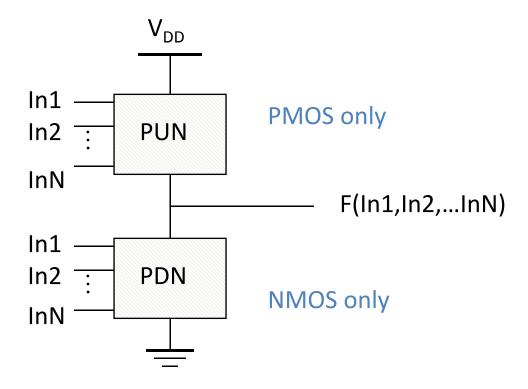

#### Static CMOS Circuit

At every point in time (except during the switching transients) each gate output is connected to either  $V_{DD}$  or  $V_{ss}$  via a low-resistive path.

The outputs of the gates assume at all times the value of the Boolean function, implemented by the circuit (ignoring, once again, the transient effects during switching periods).

This is in contrast to the dynamic circuit class, which relies on temporary storage of signal values on the capacitance of high impedance circuit nodes.

## Static Complementary CMOS

PUN and PDN are dual logic networks

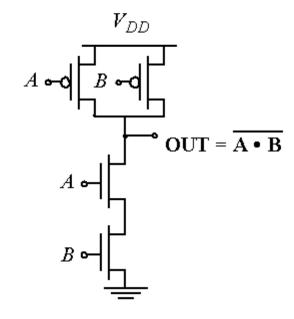

### Example Gate: NAND

| A | В | Out |

|---|---|-----|

| 0 | 0 | 1   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

Truth Table of a 2 input NAND gate

PDN:

$$G = A B \Rightarrow Conduction to GND$$

PUN:

$$F = A + B = AB \Rightarrow Conduction to V_{DD}$$

$$G(In_1,In_2,In_3,\ldots) \equiv F(\overline{In_1},\overline{In_2},\overline{In_3},\ldots)$$

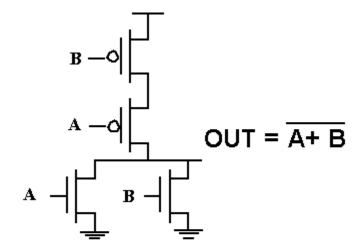

## Example Gate: NOR

|      | A       | В         | Out     |      |

|------|---------|-----------|---------|------|

|      | 0       | 0         | 1       |      |

|      | 0       | 1         | 0       |      |

|      | 1       | 0         | 0       |      |

|      | 1       | 1         | 0       |      |

| Trut | h Table | of a 2 in | put NOR | gate |

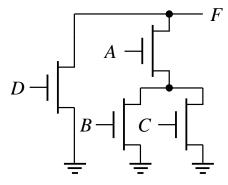

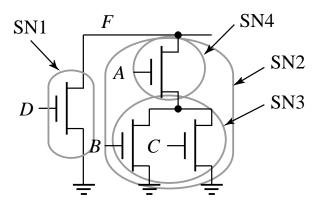

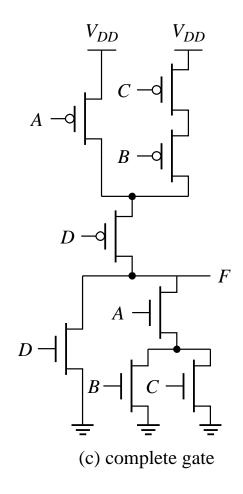

#### Constructing a Complex Gate

(a) pull-down network

(b) Deriving the pull-up network hierarchically by identifying sub-nets

#### **Properties of Complementary CMOS Gates**

High noise margins:

$V_{OH}$  and  $V_{OL}$  are at  $V_{DD}$  and GND, respectively.

No static power consumption

There never exists a direct path between  $V_{DD}^{}$  and  $V_{SS}^{}$  (GND) in steady-state mode.

Comparable rise and fall times: (under appropriate sizing conditions)

#### **CMOS** Properties

- Full rail-to-rail swing; high noise margins

- Logic levels not dependent upon the relative device sizes; ratioless

- Always a path to Vdd or Gnd in steady state; low output impedance

- Extremely high input resistance; nearly zero steady-state input current

- No direct path steady state between power and ground; no static power dissipation

- Propagation delay function of load capacitance and resistance of transistors

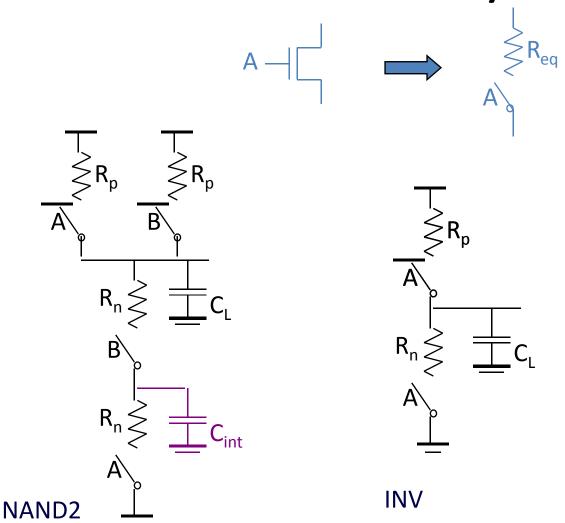

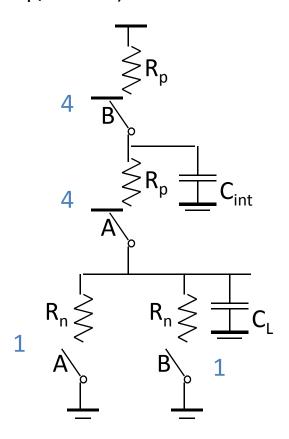

## Switch Delay Model

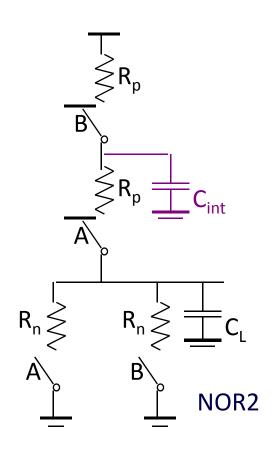

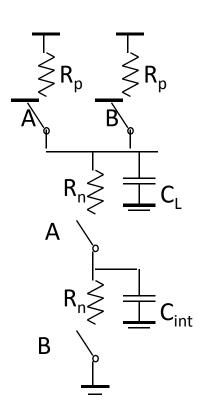

## Input Pattern Effects on Delay

(consider a NAND gate with A and B input)

- Delay is dependent on the pattern of inputs

- Low to high transition

- both inputs go low

- delay is 0.69  $R_p/2 C_L$

- one input goes low

- delay is 0.69 R<sub>p</sub> C<sub>L</sub>

- High to low transition

- both inputs go high

- delay is 0.69 2R<sub>n</sub> C<sub>L</sub>

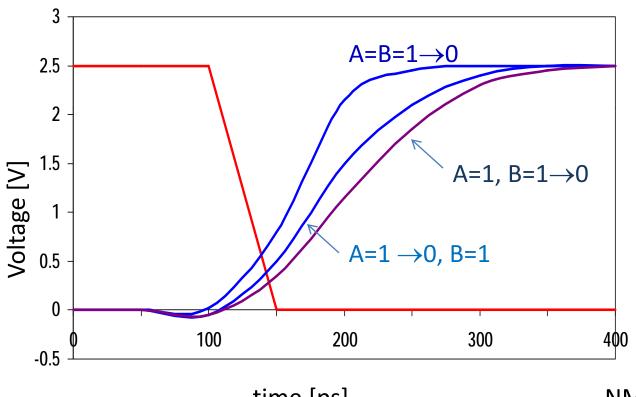

## Delay Dependence on Input Patterns

| Input Data<br>Pattern | Delay<br>(psec) |

|-----------------------|-----------------|

| A=B=0→1               | 69              |

| A=1, B=0→1            | 62              |

| A= 0→1, B=1           | 50              |

| A=B=1→0               | 35              |

| A=1, B=1→0            | 76              |

| A= 1→0, B=1           | 57              |

time [ps]

NMOS =  $0.5\mu m/0.25 \mu m$ PMOS =  $0.75\mu m/0.25 \mu m$  $C_I = 100 fF$

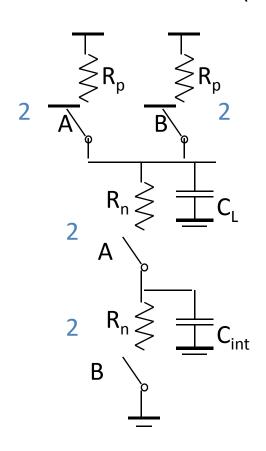

## **Transistor Sizing**

(assume inverter Wp/Wn = 2)

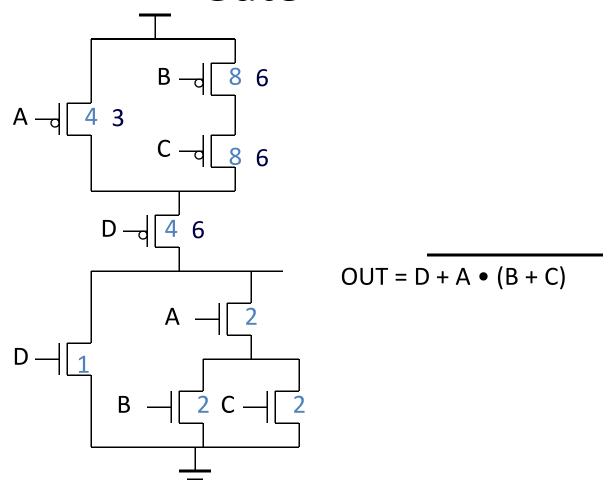

# Transistor Sizing a Complex CMOS Gate

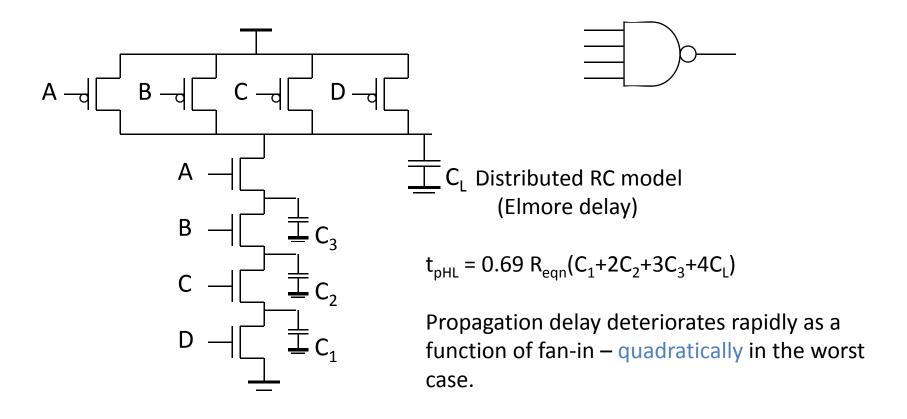

#### Fan-In Considerations

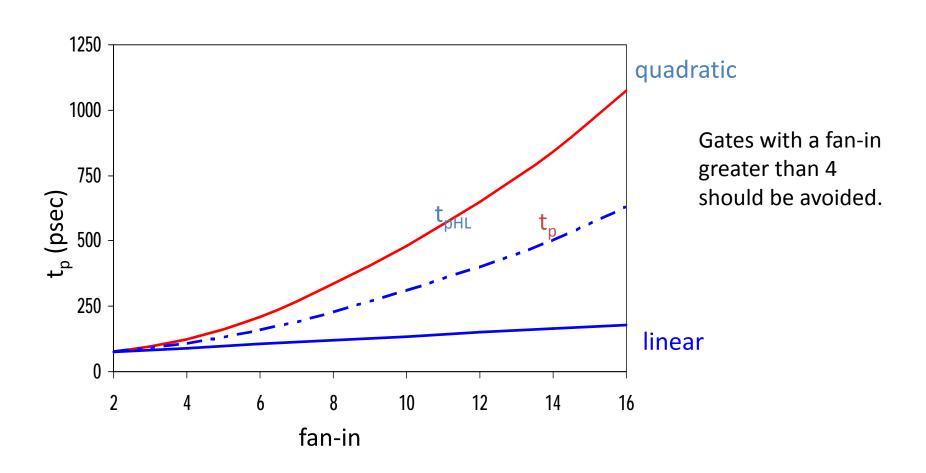

## t<sub>p</sub> as a Function of Fan-In

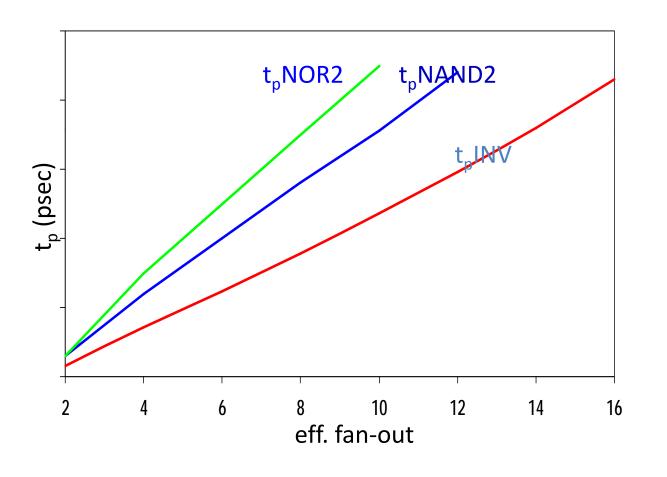

## t<sub>p</sub> as a Function of Fan-Out

All gates have the same drive current.

Slope is a function of "driving strength"

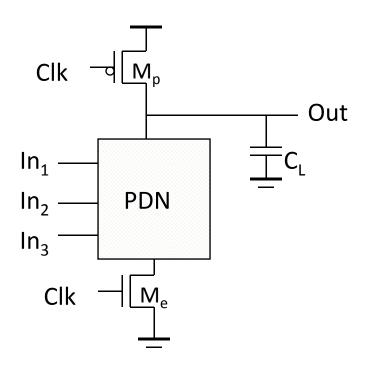

#### Dynamic CMOS

- In static circuits at every point in time (except when switching) the output is connected to either GND or V<sub>DD</sub> via a low resistance path.

- fan-in of n requires 2n (n N-type + n P-type) devices

- Dynamic circuits rely on the temporary storage of signal values on the capacitance of high impedance nodes.

- requires on n + 2 (n+1 N-type + 1 P-type) transistors

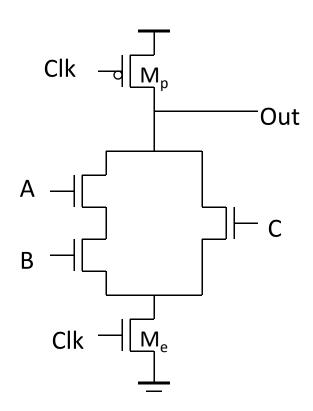

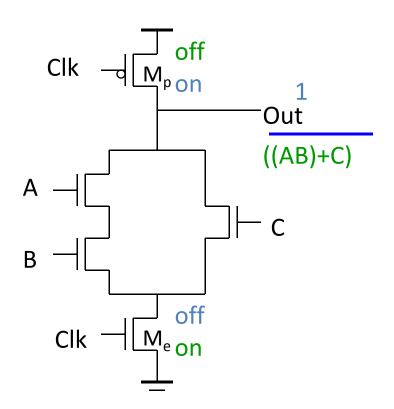

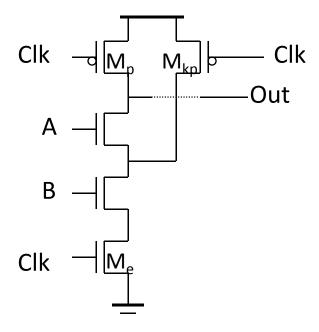

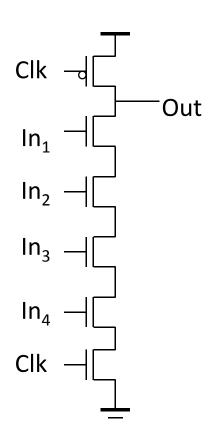

## **Dynamic Gate**

Two phase operation

Precharge (CLK = 0)

Evaluate (CLK = 1)

## **Dynamic Gate**

Two phase operation

Precharge (Clk = 0)

Evaluate (Clk = 1)

## **Properties of Dynamic Gates**

- Logic function is implemented by the PDN only

- number of transistors is N + 2 (versus 2N for static complementary CMOS)

- Full swing outputs  $(V_{OL} = GND \text{ and } V_{OH} = V_{DD})$

- Non-ratioed sizing of the devices does not affect the logic levels

- Faster switching speeds

- reduced load capacitance due to lower input capacitance (C<sub>in</sub>)

- reduced load capacitance due to smaller output loading (Cout)

- no I<sub>sc</sub>, so all the current provided by PDN goes into discharging C<sub>I</sub>

## **Properties of Dynamic Gates**

- Overall power dissipation usually higher than static CMOS

- no static current path ever exists between  $V_{DD}$  and GND (including  $P_{sc}$ )

- no glitching

- higher transition probabilities

- extra load on Clk

- PDN starts to work as soon as the input signals exceed  $V_{Tn}$ , so  $V_{M}$ ,  $V_{IH}$  and  $V_{IL}$  equal to  $V_{Tn}$

- low noise margin (NM<sub>1</sub>)

- Needs a precharge/evaluate clock

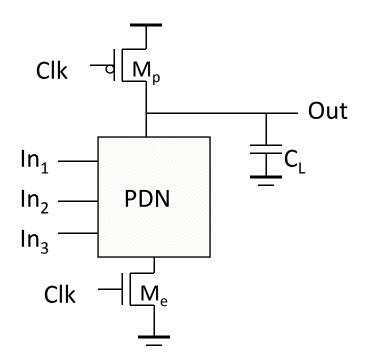

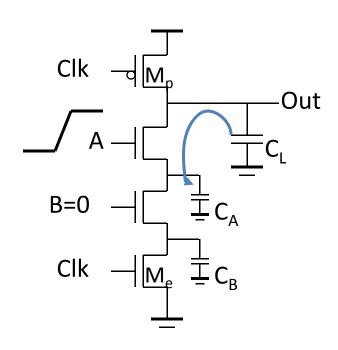

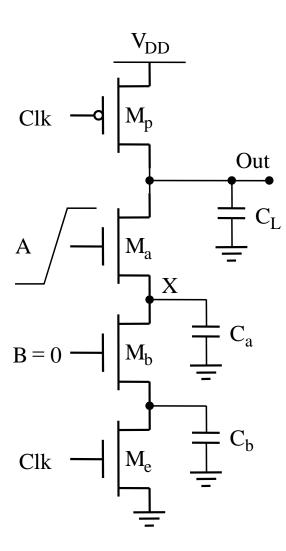

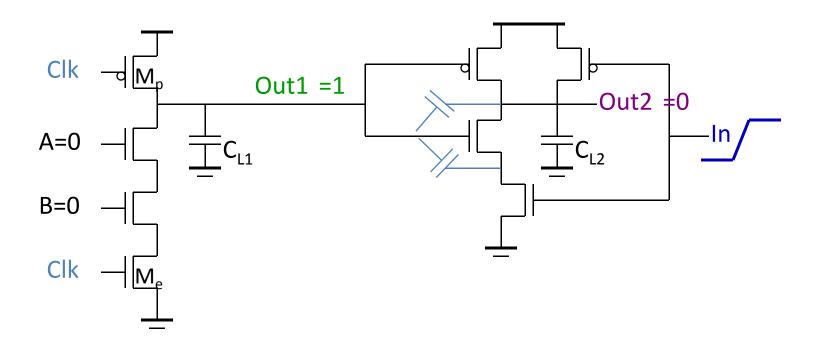

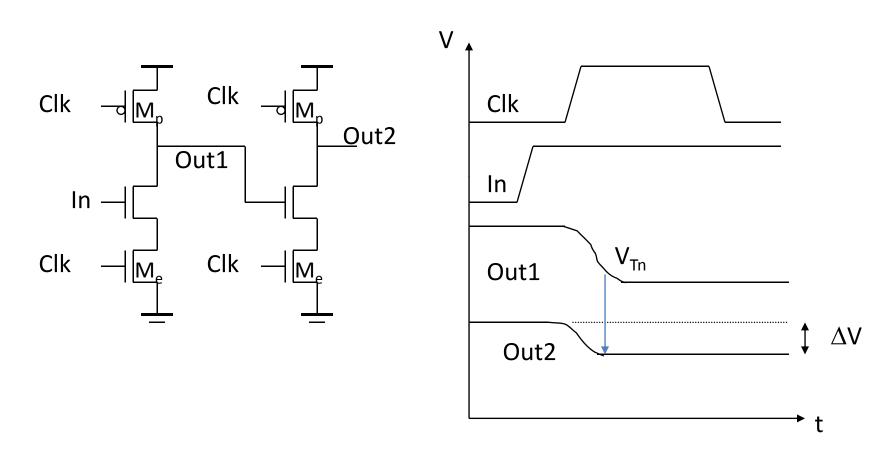

# Issues in Dynamic Design 2: Charge Sharing

Charge stored originally on  $C_L$  is redistributed (shared) over  $C_L$  and  $C_A$  leading to reduced robustness

## Charge Sharing Example

## **Charge Sharing**

case 1) if

$$\Delta V_{out} < V_{Tn}$$

$$C_L V_{DD} = C_L V_{out}(t) + C_a(V_{DD} - V_{Tn}(V_X))$$

or

or

$$\Delta V_{out} = V_{out}(t) - V_{DD} = -\frac{C_a}{C_L}(V_{DD} - V_{Tn}(V_X))$$

case 2) if

$$\Delta V_{out} > V_{Tn}$$

$$\Delta V_{out} = -V_{DD} \left( \frac{C_a}{C_a + C_L} \right)$$

## Solution to Charge Redistribution

Precharge internal nodes using a clock-driven transistor (at the cost of increased area and power)

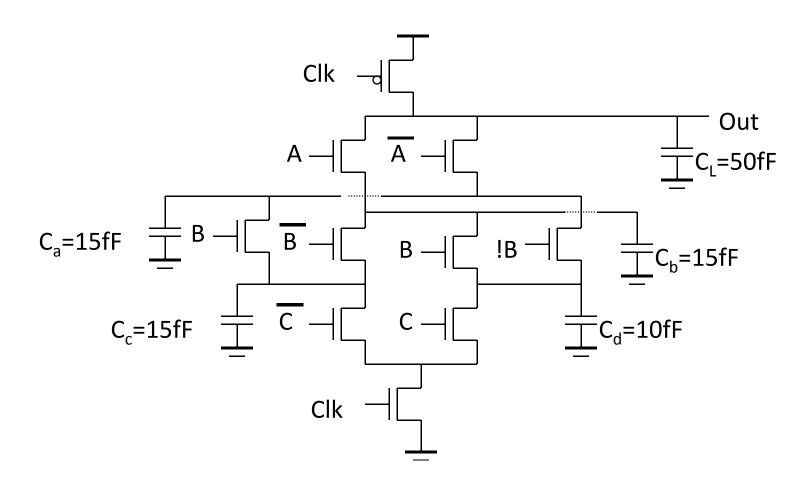

# Issues in Dynamic Design 3: Backgate Coupling

**Dynamic NAND**

Static NAND

## **Backgate Coupling Effect**

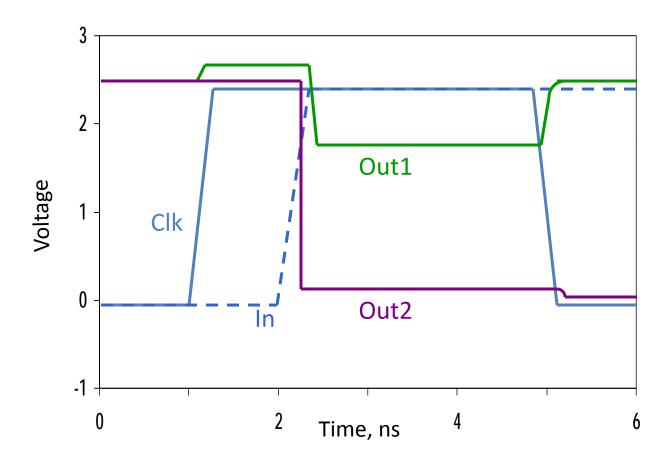

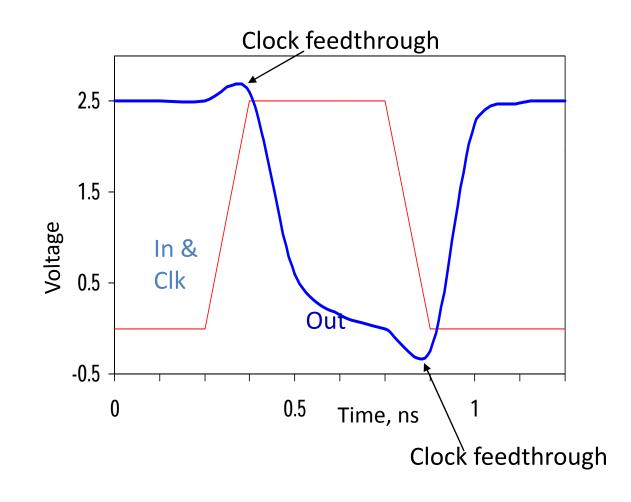

# Issues in Dynamic Design 4: Clock Feedthrough

Coupling between Out and Clk input of the precharge device due to the gate to drain capacitance. So voltage of Out can rise above  $V_{DD}$ . The fast rising (and falling edges) of the clock couple to Out.

## Clock Feedthrough

#### Other Effects

- Capacitive coupling

- Substrate coupling

- Minority charge injection

- Supply noise (ground bounce)

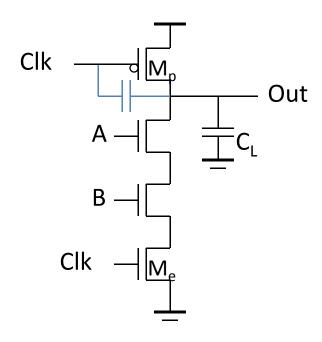

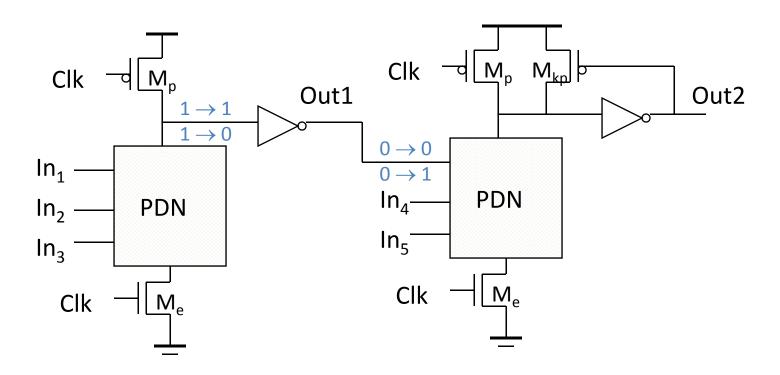

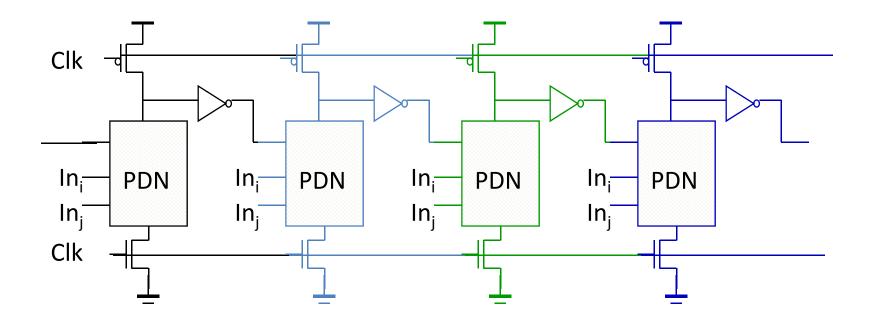

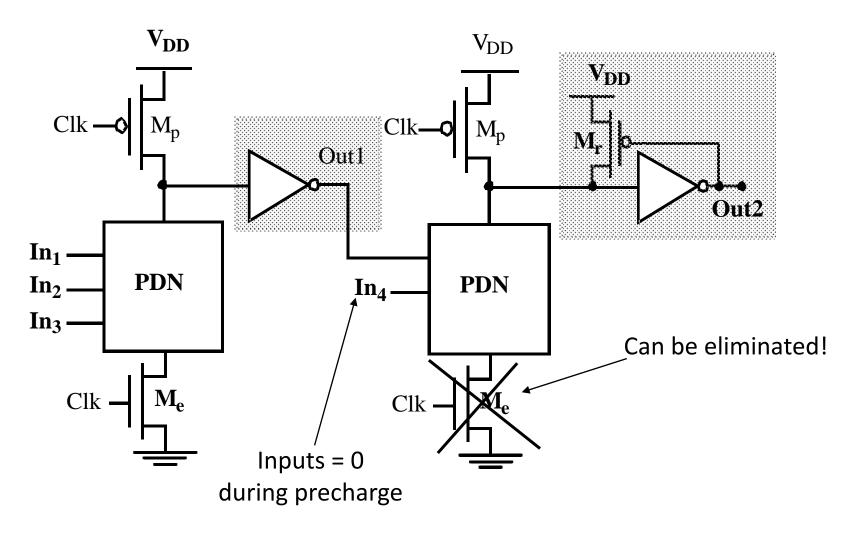

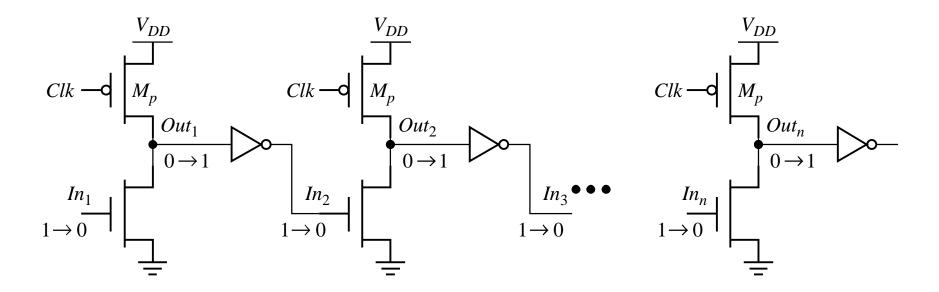

## **Cascading Dynamic Gates**

Only  $0 \rightarrow 1$  transitions allowed at inputs!

## Domino Logic

## Why Domino?

Like falling dominos!

## Properties of Domino Logic

- Only non-inverting logic can be implemented

- Very high speed

- static inverter can be skewed, only L-H transition

- Input capacitance reduced smaller logical effort

## Designing with Domino Logic

#### **Footless Domino**

The first gate in the chain needs a foot switch Precharge is rippling – short-circuit current A solution is to delay the clock for each stage